As indicated in an earlier post, the JFET is a three-terminal device with one terminal capable of controlling the current between the other two. In our discussion of the BJT transistor, the npn transistor was employed through the major part of the analysis and design sections, with a section devoted to the effect of using a PNP transistor. For the JFET transistor, the n-channel device will be the prominent device, with paragraphs and sections devoted to the effect of using a p-channel JFET.

The basic construction of the n-channel JFET is shown in below figure. Note that the major part of the structure is the n-type material, which forms the channel between the embedded layers of p-type material. The top of the n-type channel is connected through an ohmic contact to a terminal referred to as the drain (D), whereas the lower end of the same material is connected through an ohmic contact to a terminal referred to as the source (S). The two p-type materials are connected together and to the gate (G) terminal. In essence, therefore, the drain and the source are connected to the ends of the n-type channel and the gate to the two layers of p-type material. In the absence of any applied potentials, the JFET has two p–n junctions under no-bias conditions. The result is a depletion region at each junction, as shown in Fig. 3, that resembles the same region of a diode under no-bias conditions. Recall also that a depletion region is void of free carriers and is, therefore, unable to support conduction.

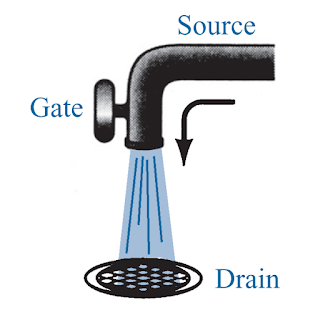

Analogies are seldom perfect and at times can be misleading, but the water analogy of below figure does provide a sense for the JFET control at the gate terminal and the appropriateness of the terminology applied to the terminals of the device. The source of water pressure can be likened to the applied voltage from drain to source, which establishes a flow of water (electrons) from the spigot (source). The “gate,” through an applied signal (potential), controls the flow of water (charge) to the “drain.” The drain and source terminals are at opposite ends of the n-channel as introduced in Fig. 3 because the terminology is defined for electron flow.

VGS = 0 volt, VDS some positive value

as shown in the next figure, a positive voltage VDS is applied across the channel and the gate is connected directly to the source to establish the condition VGS = 0 V. The result is a gate and a source terminal at the same potential and a depletion region in the low end of each p-material similar to the distribution of the no-bias conditions of above fig (very first figure of this post). The instant the voltage VDD (=VDS) is applied, the electrons are drawn to the drain terminal, establishing the conventional current ID with the defined direction of Fig. 5. The path of charge flow clearly reveals that the drain and source currents are equivalent (ID = IS).

Under the conditions in Fig. 5, the flow of charge is relatively uninhibited and is limited solely by the resistance of the n-channel between drain and source.

the resistance of the channel into the divisions appearing in Fig. 6. The current ID will establish the voltage levels through the channel as indicated on the same figure. The result is that the upper region of the p-type material will be reverse-biased by about 1.5 V, with the lower region only reverse-biased by 0.5 V. Recall from the discussion of the diode operation that the greater the applied reverse bias, the wider is the depletion region—hence the distribution of the depletion region as shown in Fig. 6. The fact that the p–n junction is reverse-biased for the length of the channel results in a gate current of zero amperes, as shown in the same figure. The fact that IG = 0 A is an important characteristic of the JFET.

As the voltage VDS is increased from 0 V to a few volts, the current will increase as determined by Ohm’s law and the plot of ID versus VDS will appear as shown in Fig. 7. The relative straightness of the plot reveals that for the region of low values of VDS, the resistance is essentially constant. As VDS increases and approaches a level referred to as VP in Fig. 7, the depletion regions of Fig. 5 will widen, causing a noticeable reduction in the channel width. The reduced path of conduction causes the resistance to increase and the curve in the graph of Fig. 7 to occur. The more horizontal the curve, the higher the resistance, suggesting that the resistance is approaching “infinite” ohms in the horizontal region. If VDS is increased to a level where it appears that the two depletion regions would

“touch” as shown in Fig. 8, a condition referred to as pinch-off will result. The level of

VDS that establishes this condition is referred to as the pinch-off voltage and is denoted by

VP, as shown in Fig. 7. In actuality, the term pinch-off is a misnomer in that it suggests

the current ID is pinched off and drops to 0 A. As shown in Fig. 7, however, this is hardly

the case— ID maintains a saturation level defined as IDSS in Fig. 7. In reality, a very small

channel still exists, with a current of very high density. The fact that ID does not drop off

at pinch-off and maintains the saturation level indicated in Fig. 7 is verified by the following fact: The absence of a drain current would remove the possibility of different potential

levels through the n-channel material to establish the varying levels of reverse bias along with

the p–n junction. The result would be a loss of the depletion region distribution that caused

pinch-off in the first place.

“touch” as shown in Fig. 8, a condition referred to as pinch-off will result. The level of

VDS that establishes this condition is referred to as the pinch-off voltage and is denoted by

VP, as shown in Fig. 7. In actuality, the term pinch-off is a misnomer in that it suggests

the current ID is pinched off and drops to 0 A. As shown in Fig. 7, however, this is hardly

the case— ID maintains a saturation level defined as IDSS in Fig. 7. In reality, a very small

channel still exists, with a current of very high density. The fact that ID does not drop off

at pinch-off and maintains the saturation level indicated in Fig. 7 is verified by the following fact: The absence of a drain current would remove the possibility of different potential

levels through the n-channel material to establish the varying levels of reverse bias along with

the p–n junction. The result would be a loss of the depletion region distribution that caused

pinch-off in the first place.

As VDS is increased beyond VP, the region of a close encounter between the two depletion

regions increases in length along the channel, but the level of ID remains essentially the

same. In essence, therefore, once VDS > VP the JFET has the characteristics of a current

source. As shown in Fig. 9, the current is fixed at ID = IDSS, but the voltage VDS (for levels

7 VP) is determined by the applied load.

As VDS is increased beyond VP, the region of a close encounter between the two depletion

regions increases in length along the channel, but the level of ID remains essentially the

same. In essence, therefore, once VDS > VP the JFET has the characteristics of a current

source. As shown in Fig. 9, the current is fixed at ID = IDSS, but the voltage VDS (for levels

7 VP) is determined by the applied load.

The choice of notation IDSS is derived from the fact that it is the drain-to-source current with a short-circuit connection from gate to source. As we continue to investigate the characteristics of the device we will find that:

IDSS is the maximum drain current for a JFET and is defined by the conditions VGS = 0 V and

VDS > | VP |.

Note in Fig. 7 that VGS = 0 V for the entire length of the curve. The next few paragraphs will describe how the characteristics of Fig. 7 are affected by changes in the level of VGS.

VGS > 0 V

The voltage from gate to source, denoted VGS, is the controlling voltage of the JFET. Just as various curves for IC versus VCE were established for different levels of IB for the BJT transistor, curves of ID versus VDS for various levels of VGS can be developed for the JFET. For the n-channel device, the controlling voltage VGS is made more and more negative from its VGS 5 0 V level. In other words, the gate terminal will be set at lower and lower potential levels as compared to the source.

In Fig. 10 a negative voltage of 21 V is applied between the gate and source terminals for a low level of VDS. The effect of the applied negative-bias VGS is to establish depletion regions similar to those obtained with VGS 5 0 V, but at lower levels of VDS. Therefore, the result of applying a negative bias to the gate is to reach the saturation level at a lower level of VDS, as shown in Fig. 11 for VGS = -1 V. The resulting saturation level for ID has been reduced and in fact will continue to decrease as VGS is made more and more negative. Note also in Fig. 11 how the pinch-off voltage continues to drop in a parabolic manner as VGS becomes more and more negative. Eventually, VGS when VGS = -VP will be sufficiently negative to establish a saturation level that is essentially 0 mA, and for all practical purposes the device has been “turned off.” In summary:

The level of VGS that results in ID 5 0 mA is defined by VGS = VP, with VP being a negative voltage for n-channel devices and a positive voltage for p-channel JFETs.

On most specification sheets the pinch-off voltage is specified as VGS(off) rather than VP. A specification sheet will be reviewed later in the chapter when the majority of the controlling elements have been introduced. The region to the right of the pinch-off locus of Fig. 11 is the region typically employed in linear amplifiers (amplifiers with minimum distortion of the applied signal) and is commonly referred to as the constant-current, saturation, or linear amplification region.

Note at high levels of VDS that the curves suddenly rise to levels that seem unbounded. The vertical rise is an indication that breakdown has occurred and the current through the channel (in the same direction as normally encountered) is now limited solely by the external circuit. Although not appearing in Fig. 11 for the n-channel device, they do occur for the n-channel device if sufficient voltage is applied. This region can be avoided if the level of VDSmax is noted on the specification sheet and the design is such that the actual level of VDS is less than this value for all values of VGS.

The graphic symbols for the n-channel and p-channel JFETs are provided in Fig. 14. Note that the arrow is pointing in for the n-channel device of Fig. 14a to represent the direction in which IG would flow if the p–n junction were forward-biased. For the p-channel device (Fig. 14b) the only difference in the symbol is the direction of the arrow in the symbol.

The basic construction of the n-channel JFET is shown in below figure. Note that the major part of the structure is the n-type material, which forms the channel between the embedded layers of p-type material. The top of the n-type channel is connected through an ohmic contact to a terminal referred to as the drain (D), whereas the lower end of the same material is connected through an ohmic contact to a terminal referred to as the source (S). The two p-type materials are connected together and to the gate (G) terminal. In essence, therefore, the drain and the source are connected to the ends of the n-type channel and the gate to the two layers of p-type material. In the absence of any applied potentials, the JFET has two p–n junctions under no-bias conditions. The result is a depletion region at each junction, as shown in Fig. 3, that resembles the same region of a diode under no-bias conditions. Recall also that a depletion region is void of free carriers and is, therefore, unable to support conduction.

Analogies are seldom perfect and at times can be misleading, but the water analogy of below figure does provide a sense for the JFET control at the gate terminal and the appropriateness of the terminology applied to the terminals of the device. The source of water pressure can be likened to the applied voltage from drain to source, which establishes a flow of water (electrons) from the spigot (source). The “gate,” through an applied signal (potential), controls the flow of water (charge) to the “drain.” The drain and source terminals are at opposite ends of the n-channel as introduced in Fig. 3 because the terminology is defined for electron flow.

VGS = 0 volt, VDS some positive value

as shown in the next figure, a positive voltage VDS is applied across the channel and the gate is connected directly to the source to establish the condition VGS = 0 V. The result is a gate and a source terminal at the same potential and a depletion region in the low end of each p-material similar to the distribution of the no-bias conditions of above fig (very first figure of this post). The instant the voltage VDD (=VDS) is applied, the electrons are drawn to the drain terminal, establishing the conventional current ID with the defined direction of Fig. 5. The path of charge flow clearly reveals that the drain and source currents are equivalent (ID = IS).

Under the conditions in Fig. 5, the flow of charge is relatively uninhibited and is limited solely by the resistance of the n-channel between drain and source.

the resistance of the channel into the divisions appearing in Fig. 6. The current ID will establish the voltage levels through the channel as indicated on the same figure. The result is that the upper region of the p-type material will be reverse-biased by about 1.5 V, with the lower region only reverse-biased by 0.5 V. Recall from the discussion of the diode operation that the greater the applied reverse bias, the wider is the depletion region—hence the distribution of the depletion region as shown in Fig. 6. The fact that the p–n junction is reverse-biased for the length of the channel results in a gate current of zero amperes, as shown in the same figure. The fact that IG = 0 A is an important characteristic of the JFET.

As the voltage VDS is increased from 0 V to a few volts, the current will increase as determined by Ohm’s law and the plot of ID versus VDS will appear as shown in Fig. 7. The relative straightness of the plot reveals that for the region of low values of VDS, the resistance is essentially constant. As VDS increases and approaches a level referred to as VP in Fig. 7, the depletion regions of Fig. 5 will widen, causing a noticeable reduction in the channel width. The reduced path of conduction causes the resistance to increase and the curve in the graph of Fig. 7 to occur. The more horizontal the curve, the higher the resistance, suggesting that the resistance is approaching “infinite” ohms in the horizontal region. If VDS is increased to a level where it appears that the two depletion regions would

“touch” as shown in Fig. 8, a condition referred to as pinch-off will result. The level of

VDS that establishes this condition is referred to as the pinch-off voltage and is denoted by

VP, as shown in Fig. 7. In actuality, the term pinch-off is a misnomer in that it suggests

the current ID is pinched off and drops to 0 A. As shown in Fig. 7, however, this is hardly

the case— ID maintains a saturation level defined as IDSS in Fig. 7. In reality, a very small

channel still exists, with a current of very high density. The fact that ID does not drop off

at pinch-off and maintains the saturation level indicated in Fig. 7 is verified by the following fact: The absence of a drain current would remove the possibility of different potential

levels through the n-channel material to establish the varying levels of reverse bias along with

the p–n junction. The result would be a loss of the depletion region distribution that caused

pinch-off in the first place.

“touch” as shown in Fig. 8, a condition referred to as pinch-off will result. The level of

VDS that establishes this condition is referred to as the pinch-off voltage and is denoted by

VP, as shown in Fig. 7. In actuality, the term pinch-off is a misnomer in that it suggests

the current ID is pinched off and drops to 0 A. As shown in Fig. 7, however, this is hardly

the case— ID maintains a saturation level defined as IDSS in Fig. 7. In reality, a very small

channel still exists, with a current of very high density. The fact that ID does not drop off

at pinch-off and maintains the saturation level indicated in Fig. 7 is verified by the following fact: The absence of a drain current would remove the possibility of different potential

levels through the n-channel material to establish the varying levels of reverse bias along with

the p–n junction. The result would be a loss of the depletion region distribution that caused

pinch-off in the first place. As VDS is increased beyond VP, the region of a close encounter between the two depletion

regions increases in length along the channel, but the level of ID remains essentially the

same. In essence, therefore, once VDS > VP the JFET has the characteristics of a current

source. As shown in Fig. 9, the current is fixed at ID = IDSS, but the voltage VDS (for levels

7 VP) is determined by the applied load.

As VDS is increased beyond VP, the region of a close encounter between the two depletion

regions increases in length along the channel, but the level of ID remains essentially the

same. In essence, therefore, once VDS > VP the JFET has the characteristics of a current

source. As shown in Fig. 9, the current is fixed at ID = IDSS, but the voltage VDS (for levels

7 VP) is determined by the applied load.The choice of notation IDSS is derived from the fact that it is the drain-to-source current with a short-circuit connection from gate to source. As we continue to investigate the characteristics of the device we will find that:

IDSS is the maximum drain current for a JFET and is defined by the conditions VGS = 0 V and

VDS > | VP |.

Note in Fig. 7 that VGS = 0 V for the entire length of the curve. The next few paragraphs will describe how the characteristics of Fig. 7 are affected by changes in the level of VGS.

VGS > 0 V

The voltage from gate to source, denoted VGS, is the controlling voltage of the JFET. Just as various curves for IC versus VCE were established for different levels of IB for the BJT transistor, curves of ID versus VDS for various levels of VGS can be developed for the JFET. For the n-channel device, the controlling voltage VGS is made more and more negative from its VGS 5 0 V level. In other words, the gate terminal will be set at lower and lower potential levels as compared to the source.

In Fig. 10 a negative voltage of 21 V is applied between the gate and source terminals for a low level of VDS. The effect of the applied negative-bias VGS is to establish depletion regions similar to those obtained with VGS 5 0 V, but at lower levels of VDS. Therefore, the result of applying a negative bias to the gate is to reach the saturation level at a lower level of VDS, as shown in Fig. 11 for VGS = -1 V. The resulting saturation level for ID has been reduced and in fact will continue to decrease as VGS is made more and more negative. Note also in Fig. 11 how the pinch-off voltage continues to drop in a parabolic manner as VGS becomes more and more negative. Eventually, VGS when VGS = -VP will be sufficiently negative to establish a saturation level that is essentially 0 mA, and for all practical purposes the device has been “turned off.” In summary:

The level of VGS that results in ID 5 0 mA is defined by VGS = VP, with VP being a negative voltage for n-channel devices and a positive voltage for p-channel JFETs.

On most specification sheets the pinch-off voltage is specified as VGS(off) rather than VP. A specification sheet will be reviewed later in the chapter when the majority of the controlling elements have been introduced. The region to the right of the pinch-off locus of Fig. 11 is the region typically employed in linear amplifiers (amplifiers with minimum distortion of the applied signal) and is commonly referred to as the constant-current, saturation, or linear amplification region.

voltage-Controlled resistor:

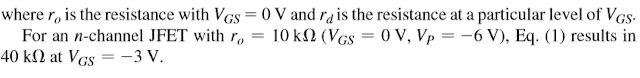

The region to the left of the pinch-off locus of Fig. 11 is referred to as the ohmic or voltage-controlled resistance region. In this region, the JFET can actually be employed as a variable resistor (possibly for an automatic gain control system) whose resistance is controlled by the applied gate-to-source voltage. Note in Fig. 11 that the slope of each curve and therefore the resistance of the device between drain and source for VDS 6 VP are a function of the applied voltage VGS. As VGS becomes more and more negative, the slope of each curve becomes more and more horizontal, corresponding to an increasing resistance level. The following equation provides a good first approximation to the resistance level in terms of the applied voltage VGS:

p-Channel devices:

The p-channel JFET is constructed in exactly the same manner as the n-channel device of Fig. 3 but with a reversal of the p- and n-type materials as shown in Fig. 12. The defined current directions are reversed, as are the actual polarities for the voltages VGS and VDS. For the p-channel device, the channel will be constricted by increasing positive voltages from gate to source and the double-subscript notation for VDS will result in negative voltages for VDS on the characteristics of Fig. 13, which has an IDSS of 6 mA and a pinch-off voltage of VGS = +6 V. Do not let the minus signs for VDS confuse you. They simply indicate that the source is at a higher potential than the drain.

Note at high levels of VDS that the curves suddenly rise to levels that seem unbounded. The vertical rise is an indication that breakdown has occurred and the current through the channel (in the same direction as normally encountered) is now limited solely by the external circuit. Although not appearing in Fig. 11 for the n-channel device, they do occur for the n-channel device if sufficient voltage is applied. This region can be avoided if the level of VDSmax is noted on the specification sheet and the design is such that the actual level of VDS is less than this value for all values of VGS.

symbols:

The graphic symbols for the n-channel and p-channel JFETs are provided in Fig. 14. Note that the arrow is pointing in for the n-channel device of Fig. 14a to represent the direction in which IG would flow if the p–n junction were forward-biased. For the p-channel device (Fig. 14b) the only difference in the symbol is the direction of the arrow in the symbol.

Comments

Post a Comment